| 事例名称 |

アナログデジタル混在ICを搭載した回路で、出力に多量のジッタが発生した |

| 代表図 |

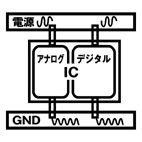

|

| 事例概要 |

アナログデジタル混在ICを搭載した回路で、出力に多量のジッタが発生した。スイッチングレギュレータ電源のノイズがIC内のPLL回路(Phase Locked Loop)に影響したためである。対策として、電源とGNDをアナログ用とデジタル用に分離した。 |

| 事象 |

アナログデジタル混在ICを搭載した回路で、出力に多量のジッタが発生した。 |

| 経過 |

図1のような、アナログデジタル混在ICを搭載した回路を試作した。装置に実装し動作確認したところ、出力に多量のジッタ(波形のゆれ)が発生した。電源にはノイズフィルタを挿入していた。また、装置搭載前の評価では、安定化電源を用いて極めてノイズの少ない環境で行い、合格していた。電源ノイズのスペクトル分析で、ノイズ周波数を解明した。 |

| 原因 |

実際の装置の電源(+5V)は、スイッチングレギュレータだったので、この電源のノイズがIC内のPLL回路に影響したためである。また、電源のノイズフィルタは、ノイズの周波数帯域と異なっていた。 |

| 対策 |

図2のように、電源とGNDをアナログ用とデジタル用に分離した。 |

| 知識化 |

PLL回路のようなアナログ回路とデジタル回路混在ICの電源は、電源を分離し、アナログ回路電源にノイズが乗らないようにする。また、ノイズフィルタは、ノイズの周波数を把握して使うべきである。 |

| 背景 |

PLL回路とは、入力信号や基準周波数と、出力信号との周波数を一致させる電子回路である。入力信号と出力信号との位相差を検出し、VCO(電圧によって周波数を変化させる発振器)や回路のループを制御することで、正確に同期した周波数の信号を発信することができる。発信周波数を一定に保つ他、カウンタを組み込むことで入力信号の整数倍の周波数で信号を出力することもできる。 |

| シナリオ |

| 主シナリオ

|

調査・検討の不足、仮想演習不足、調査・検討の不足、事前検討不足、審査・見直し不足、回路、電源、ノイズフィルタ、特性、ジッタ

|

|

| 情報源 |

創造設計エンジンDB

http://e-words.jp/w/pll.html

|

| マルチメディアファイル |

図1.アナログデジタル混在IC回路(対策前)

|

|

図2.アナログデジタル混在IC回路(対策後)

|

| 分野 |

機械

|

| データ作成者 |

張田吉昭 (有限会社フローネット)

|